## PAMS Technical Documentation NSD–1 Series Transceivers

# **System Module**

## AMENDMENT RECORD SHEET

| Amendment<br>Number | Date  | Inserted By | Comments                                            |

|---------------------|-------|-------------|-----------------------------------------------------|

|                     | 09/99 |             | Issue 1                                             |

| Issue 2             | 09/00 | OJuntune    | New variant NSD–1AW<br>updated pages 1, 2, 4, 5, 12 |

|                     |       |             |                                                     |

|                     |       |             |                                                     |

|                     |       |             |                                                     |

|                     |       |             |                                                     |

## CONTENTS

## Page No

| Transceiver NSD-1           | 5  |

|-----------------------------|----|

| Introduction                | 5  |

| Modes of Operation          | 5  |

| Interconnection Diagram     | 6  |

| System Module               | 7  |

| Circuit Description         | 7  |

| Connectors                  | 7  |

| System Connector            | 7  |

| RF–Connector                | 9  |

| Baseband Module             | 10 |

| Block Diagram               | 10 |

| •                           | 10 |

|                             | 10 |

|                             | 10 |

| CAFÉ                        | 10 |

|                             | 11 |

| PENTA                       | 11 |

| CHAPS                       | 11 |

|                             | 12 |

|                             | 12 |

| Baseband Power Distribution | 13 |

| Description                 | 13 |

|                             | 14 |

|                             | 14 |

|                             | 14 |

|                             | 15 |

|                             | 18 |

| Power Down                                                     | 21 |

|----------------------------------------------------------------|----|

| RF to Baseband Interface                                       | 22 |

| Audio control                                                  | 23 |

| Digital control                                                | 24 |

| MAD4                                                           | 24 |

| MAD Interfaces                                                 | 24 |

| Signal Definitions                                             | 25 |

| CAFE Submodule                                                 | 31 |

|                                                                | 33 |

| EMC Strategy                                                   | 34 |

| RF Module                                                      | 35 |

| Transmitter                                                    | 35 |

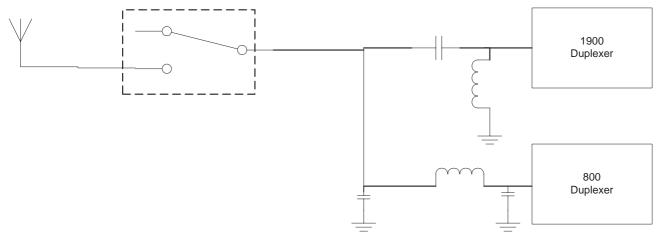

| Antenna                                                        | 35 |

| Diplexer                                                       | 35 |

| 1900 MHz Transmitter                                           | 35 |

| 1900MHz Duplexer Scorpion                                      | 35 |

| 1900 MHz Isolator                                              | 35 |

| 1900 MHz Power Amplifiers Snapper                              | 36 |

| 1900 MHz Transmitter Interstage Filtering                      | 36 |

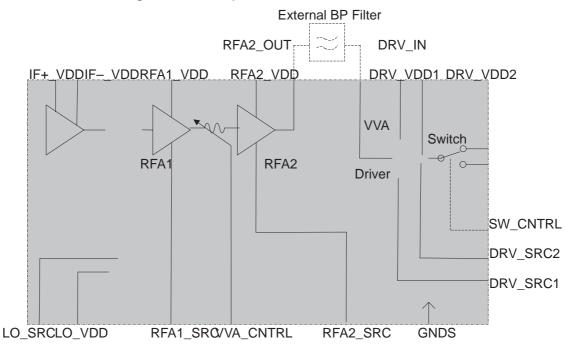

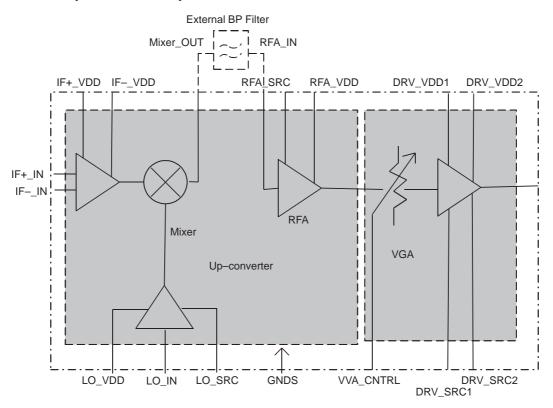

| 1900 MHz Transmitter Up–converter Apache                       | 36 |

| 800 MHz Transmitter                                            | 37 |

| 800 MHz SAW Duplexer                                           | 37 |

| 800 MHz Isolator                                               | 38 |

| 800 MHz Power Amplifiers Shark                                 | 38 |

| 800 MHz Transmitter Up–converter Odyssey                       | 38 |

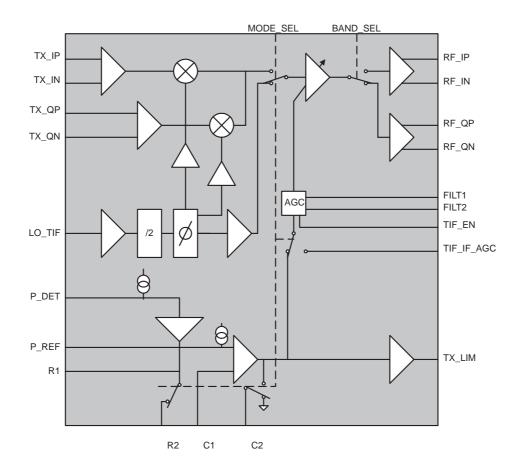

| 800 MHz and 1900 MHz Transmitter Intermediate Frequency (TIF). | 39 |

| 1900 MHz Receiver                                              | 40 |

| 1900 MHz LNA and Interstage Filter                             | 40 |

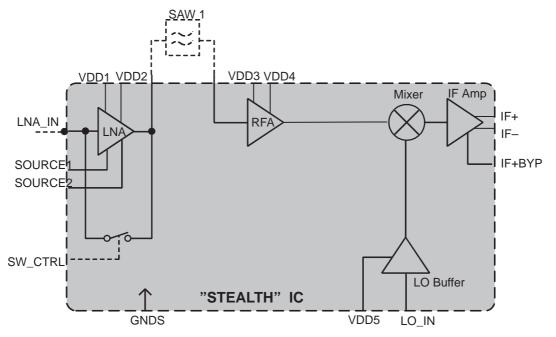

| 1900 MHz Down Converter IC STEALTH                             | 40 |

| 800 MHz and 1900 MHz CDMA IF filter                            | 41 |

| 800 MHz Receiver                                               | 41 |

| 800 MHz Down Converter IC VOYAGER                              | 42 |

| 800 MHz AMPS IF Filter                                         | 42 |

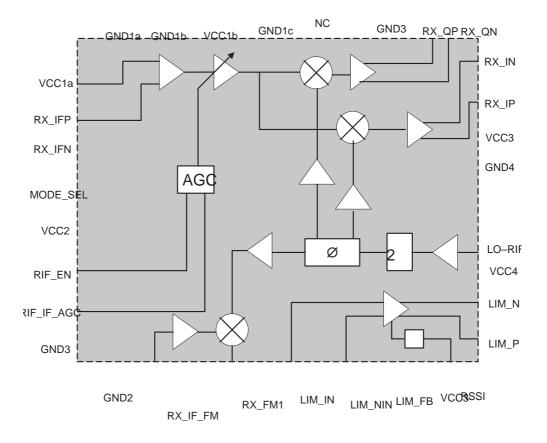

| Receiver Intermediate Frequency (RIF)                          | 42 |

| CDMA AGC                                                       | 43 |

| IQ Demodulator                                                 | 43 |

| AMPS Second Down conversion                                    | 43 |

| AMPS Limiter                                                   | 43 |

| Synthesizers                                                   | 43 |

| UHF LOs 1 GHz and 2 GHz                                        | 44 |

|                                                                | 44 |

| Transmitter VHF LO                                             | 44 |

| RF – Base Band Connections                                     | 45 |

**Schematic Diagrams:** UF4D (A3 size, at the back of the binder)

| <b>RF Block Diagram</b> |  | A–1 |

|-------------------------|--|-----|

|-------------------------|--|-----|

| BB-RF interface (Version 20a Edit 3) for layout version 20                               | A–2  |

|------------------------------------------------------------------------------------------|------|

| Circuit Diagram of Baseband (Version 20a Edit 3) layout version 20                       | A–3  |

| Circuit Diagram of Power Supply (Version 20a Edit 9) layout 20                           | A-4  |

| Circuit Diagram of RF Block (Version 20 Edit 3) layout version 20                        | A–5  |

| Circuit Diagram of RX (Version 20a Edit 4) for layout version 20                         | A–6  |

| Circuit Diagram of TX (Version 20a Edit 8) for layout version 20                         | A–7  |

| Circuit Diagram of Synthesizer (Version 20a Edit 5) layout 20                            | A–8  |

| Circuit Diagram of Cafe (Version 20a Edit 5) for layout version 20                       | A–9  |

| Circuit Diagram of MAD4 (Version 20a Edit 4) for layout version 20                       | A–10 |

| Circuit Diagram of MAD4 External Memories (V.20a Edit 4) layout 20                       | A–11 |

| Layout Diagram of UF4D – Top (Version 20)                                                | A–12 |

| Layout Diagram of UF4D – Bottom (Version 20)                                             | A–12 |

| RF Troubleshooting Test Points for UF4D – Top (Version 20) .                             | A–13 |

| RF Troubleshooting Test Points for UF4D – Bottom (Version 20)                            | A–13 |

| Schematic Diagrams: UF4I (A3 size, at the back of the binder)                            |      |

| RF Block diagram v.24                                                                    | A–14 |

| BB–RF interface (Version 06.0 Edition 8) for layout version 24                           | A–15 |

| Block Diagram of BB (Version 06.0 Edition 9) for layout version 24                       | A–16 |

| Circuit Diagram of Power Supply (Version 06.0 Edition 8) for layout version 24           | A–17 |

| Circuit Diagram of RX (Version 06.0 Edition 10) for layout version 24                    | A–18 |

| Circuit Diagram of TX (Version 06.0 Edition 8) for layout version 24                     | A–19 |

| Circuit Diagram of Synthesizer (Version 06.0 Edition 5) for layout version 24            | A–20 |

| Circuit Diagram of Cafe (Version 06.0 Edition 8) for layout version 24                   | A–21 |

| Circuit Diagram of MAD4 (Version 06.0 Edition 8) for layout version 24                   | A–22 |

| Circuit Diagram of MAD4 External Memories (Version 06.0 Edition 4) for layout version 24 | A–23 |

| Layout Diagram of UF4I – Top (issue 5.0, Version 24)                                     | A–24 |

| Layout Diagram of UF4I – Bottom (issue 5.0, Version 24)                                  | A–24 |

|                                                                                          |      |

## **Transceiver NSD-1**

## Introduction

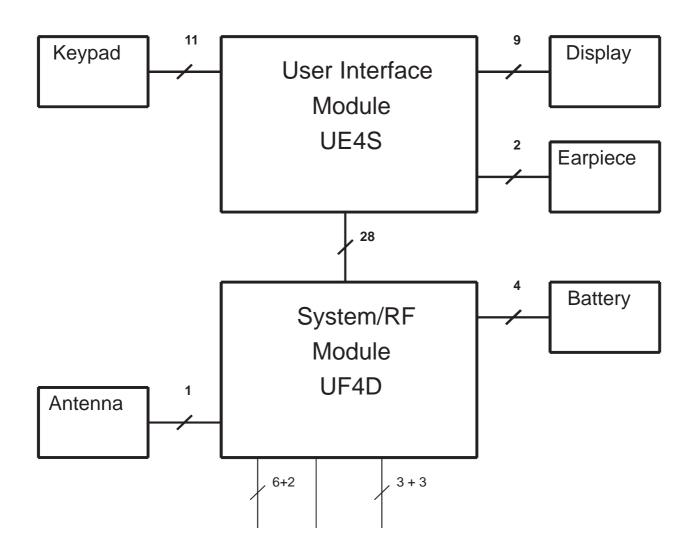

The NSD-1 is a radio transceiver unit for the CDMA 800/1900MHz and AMPS networks. The transceiver is true 3 V transceiver. The transceiver consists of System/RF module (UF4D/UF4I), User interface module (UE4) and assembly parts.

## NOTE: This System Module section describes all NSD–1 transceiver types. Keep this in mind when reading the document.

The transceiver is true 3 V transceiver. The transceiver consists of System/RF module ( UF4D ), User interface module ( UE4S ) and assembly parts.

The transceiver has leakage tolerant earpiece.

The antenna is either fixed or extendable according to the phone type.

External antenna connection is provided by rear RF connector

#### Modes of Operation

There are five different operation modes:

- power off mode

- idle mode

- active mode

- charge mode

- local mode

In the power off mode only the circuits needed for power up are supplied.

In the idle mode circuits are powered down and only sleep clock is running.

In the active mode all the circuits are supplied with power although some parts might be in the idle state part of the time.

The charge mode is effective in parallel with all previous modes. The charge mode itself consists of two different state: charge and maintenance mode.

The local mode is used for alignment and testing.

## **Interconnection Diagram**

## System Module

## **Circuit Description**

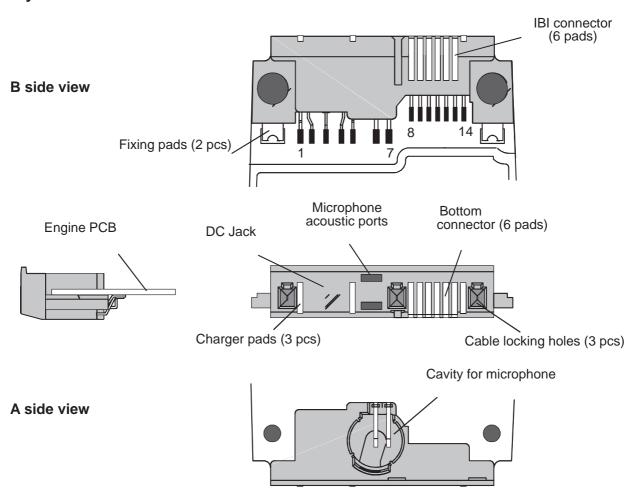

The transceiver electronics consist of the Radio Module, RF + System blocks, the UI PCB, the display module and audio components. The keypad and the display module are connected to the Radio Module with a connectors. System blocks and RF blocks are interconnected with PCB wiring. The Transceiver is connected to accessories via a bottom system connector with charging and accessory control.

The RF block is designed for a handportable phone to receive and demodulate the radio frequency signal from the base station and to transmit a modulated RF signal to the base station.

#### Connectors

Note: Intelligent Battery Interface, IBI, is an accessory interface on the battery side of the phone including the same signals as the bottom connector. The accessory (e.g. an IBI accessory) can be a battery pack with special features or an accessory module attached between the phone and a normal battery pack.

#### System Connector

| Pin | Name      | Function                     | Description                       |

|-----|-----------|------------------------------|-----------------------------------|

| 1   | V_IN      | Bottom char-<br>ger contacts | Charging voltage.                 |

| 2   | L_GND     | DC Jack                      | Logic and charging ground.        |

| 3   | V_IN      | DC Jack                      | Charging voltage.                 |

| 4   | CHRG_CTRL | DC Jack                      | Charger control.                  |

| 5   | CHRG_CTRL | Bottom char-<br>ger contacts | Charger control.                  |

| 6   | MICP      | Microphone                   | Microphone signal, positive node. |

| 7   | MICN      | Microphone                   | Microphone signal, negative node. |

| 8   | XMIC      | Bottom & IBI connectors      | Analog audio input.               |

| 9   | SGND      | Bottom & IBI connectors      | Audio signal ground.              |

| 10  | XEAR      | Bottom & IBI connectors      | Analog audio output.              |

| 11  | MBUS      | Bottom & IBI connectors      | Bidirectional serial bus.         |

| 12  | FBUS_RX   | Bottom & IBI connectors      | Serial data in.                   |

| 13  | FBUS_TX   | Bottom & IBI connectors      | Serial data out.                  |

| 14  | L_GND     | Bottom char-<br>ger contacts | Logic and charging ground.        |

#### **RF–Connector**

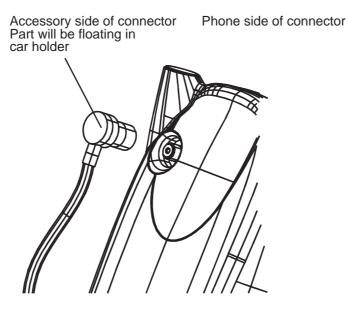

The RF–connector is needed to utilize the external antenna with Car Cradle. The RF–connector is located on the back side of the transceiver on the top section. The connector is plug type connector with special mechanical switching.

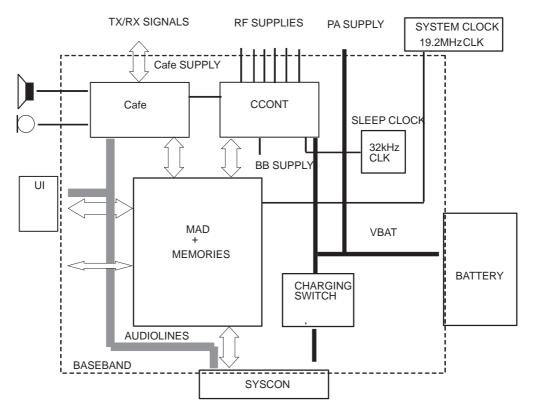

## **Baseband Module**

## **Block Diagram**

#### **Baseband Elements**

Baseband refers to all technology elements in the phone design, which do not include RF functions. The Baseband Module therefore includes audio, logic control, signal processing, power supply, and user interface functions. Baseband functionality of this product consists of third generation Digital Core Technology (DCT3) design solutions.

#### **Baseband ASICS Description**

#### MAD4

The MAD4 ASIC contains three main components: DSP, MCU, and CDMA core logic along with other functions such as User Interface. This ASIC controls logic functions for the user interface, USART and PWMs, CAFÉ, Control Timing and Interrupts (CTI), RX Modem, RF Interface, Accessory Interface, and CDMA functionality.

The DSP controls the RF power and implements the compressor and expander for AMPS, the vocoders for CDMA and DTMF tone generation.

The MCU performs tasks such as UI control, timers, PUP control, RX Modem interface, audio control, evaluation of sensor data from CCONT A\D, and battery charging control. There are three versions of MAD4. The first version has 80k words of onchip DSP RAM. The second version has 16k words of on-chip DSP RAM and 80k words of on-chip DSP ROM. The third version has an area optimized version with 16k words of on-chip DSP RAM and 80k words of onchip DSP ROM.

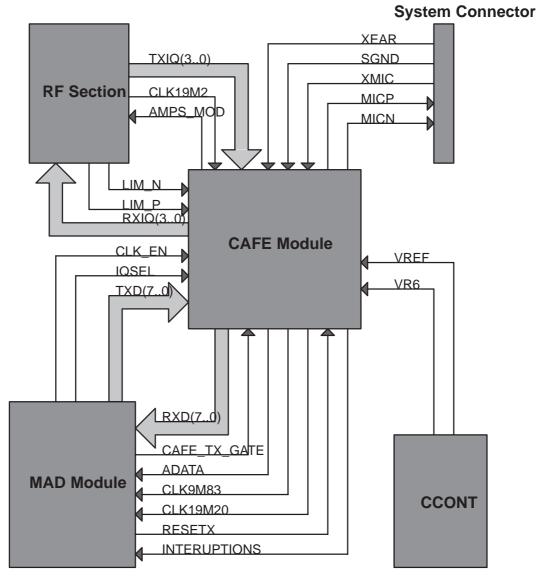

#### CAFÉ

The CAFÉ ASIC provides CODEC functionality (A/D and D/A conversions for voice data, microphone and speaker amplification, variable RX and TX Audio Gain), provides system clock squaring, utilizes PLL for CDMA clock generation from system clock, and interfaces to the RF section and to MAD4.

#### CCONT

The CCONT ASIC provides linear regulated power to most of the phone. It has a multiplexed A/D converter for temperature sensor digitization, battery voltage, charger voltage, current consumption, and battery type detection. An external 32 kHz oscillator circuit is connected to CCONT, which is used for sleep clock generation. It also has a watchdog circuit used to power off the phone in the event that MCU receives an interrupt from power key depression, or an event has caused a process to over run and MCU does not service the register to prevent the watchdog timer from timing out.

#### PENTA

The PENTA IC chip operates as a low noise, low drop out regulator with 5 independent 2.8–volt outputs used to power on various sections of the RF module. The PENTA IC has 5 control inputs are controlled by the MAD4 ASIC.

#### CHAPS

CHAPS operates as an integrated power switch for controlling charger current. Its features are limited start up current, limited maximum switch current, transient voltage protection, voltage limit protection, and reverse voltage protection. It is designed to be used with either a single lithium cell or three nickel cells battery types.

## Memories

#### SRAM

External SRAM is used by MAD4. Size is 2 Mbit (256k x 8 bit).

#### FLASH MEMORY

Flash memory contains the main program code for the MCU and default EEPROM values. Refer to the table below.

#### EEPROM

An EEPROM is used to store user data and tuning parameters. Refer to the table below.

|                                     | FLASH memory           | EEPROM memory       |

|-------------------------------------|------------------------|---------------------|

| NSD–1FX, 1GX,<br>(Nokia 5180, 5170) | 8 Mbit (1Mx16 bit)     | 256 kbit (32x8 bit) |

| NSD–1AW (5185)                      | 16 Mbit (512 x 16 bit) | 512 kbit (64x8 bit) |

## Clocks

#### System Clock and CDMA Clock

A 19.2 MHz signal is passed to the CAFÉ ASIC from the RF section. The CAFÉ then generates the 19.2 MHz system clock and the 9.8304 MHz CDMA clock, which are derived from the RF signal. Both of these clocks are passed to MAD4.

#### 8kHz Frame Sync Clock

An 8 kHz frame sync is generated in MAD4 and passed to the CAFÉ in order to synchronize the internal CAFÉ clocks with the equivalent MAD4 clocks. This signal is also used to "frame" the CODEC voice data at 8kHz. The pulse width of the frame sync will be equal to one period of the 320 kHz clock, which is internal to CAFÉ.

#### Sleep Clock

Sleep clock is provided by CCONT and produces a 32.768 kHz clock used by MAD4 when it is in sleep mode. The crystal oscillator in the external CCONT circuitry to CCONT is not automatically started when the battery is connected, but after power up the oscillator is always running, even during power off periods. The only exception is when the battery is removed.

#### UIF and CCONT Serial Clock (UIF\_CCONT\_SCLK)

This 960 KHz clock is used to synchronize serial data transmission on the UIF and CCONT serial data bus UIF\_CCONT\_SDIO.

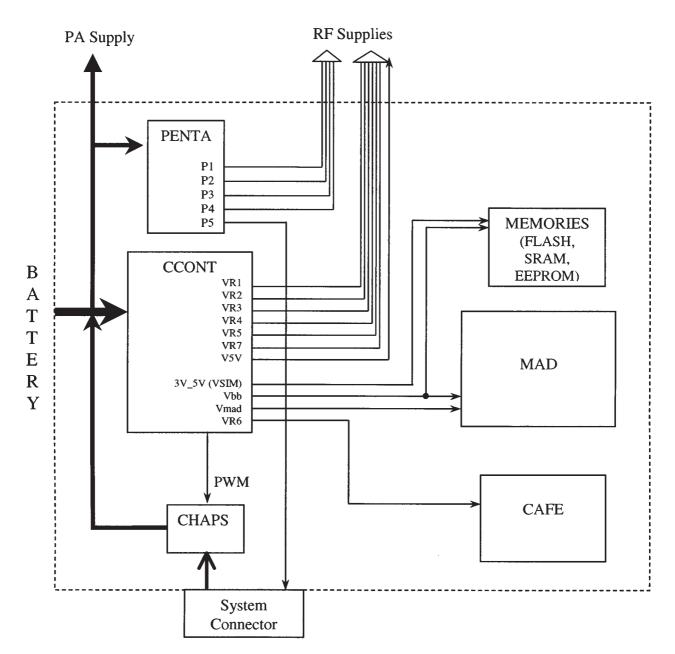

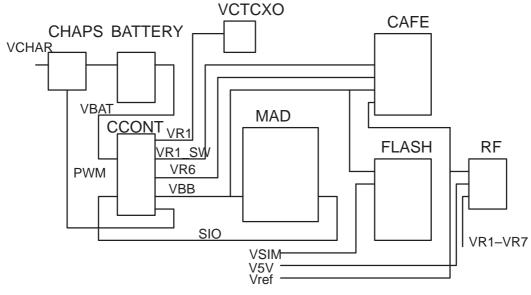

## **Baseband Power Distribution**

#### Description

Power management and distribution in the phone is handled by the CCONT asic. CCONT is a multi function power management IC which has seven 2.8V linear regulators for the RF–section of the phone. One 2.8V regulator is used to power up the baseband of the phone, and its output is called Vbb. Additionally, one adjustable regulator is used to power up certain parts of the baseband. There are also a 5V charge pump, 5V regulator and 3/5V regulator.

The main functions are voltage regulation, power up/down procedures, reset logic, charging control (PWM), watchdog, sleep control, ADC and real time clock.

#### **CCONT Regulators**

Battery voltage VBAT is connected to CCONT which regulates all the supply voltages VBB, VR1–VR7, V2V, VR1\_SW, VSIM and V5V. CCONT's default startup mode is to turn on VR1, VBB, V2V, VR6 and Vref in power–up. Vrefs default value is 1.5V, but in in this phone we use 1.25V for Vref, so one of the first things MAD4 does on power up is to do a write to CCONT to change Vref to 1.25V.

VBB is used as baseband power supply for all digital parts, and it is on whenever the phone is powered up. V2V is reserved for a later version of the MAD4 ASIC which will have a lower core voltage. When the low voltage core version of MAD4 is available, V2V will be connected to those pins on MAD4 which power the core. VSIM is used as programming voltage for the Flash memory after the phone is cut out of the panel. This is necessary if re–flashing is needed after initial flash programming in production. V5V is used for RF parts only. VR6 supplies the power for CAFE.

VR1 is used for the VCTCXO supply. VR1\_SW is derived from VR1 inside CCONT, and is actually the same voltage, but can be separately switched on and off. This VR1\_SW is used as an optional external microphone bias voltage. CLK\_EN signal to CCONT controls both the VR1 and VR6 regulators; they can be switched off in sleep modes, during standby.

CCONT regulators are controlled through a seial data bus from MAD4. Regulators VR3, 4, 5 and 7 are controllable through external pins; these pins forming a logical 'OR' function with the serial commands. If a regulator's control pin is at logic '1', that regulator will turn on. If the pins are not used for external control they are grounded.

Most of the regulator outputs depend on pin control. In the table the 'State in reset' is based on assumption that pin controls are '0'.

#### Charging

Charging can be performed in any operating mode. The charging algorithm is dependent on the battery technology used. A resistor internal to the battery pack indicates the battery type. The resistor value corresponds to a specific battery capacity. This capacity value is related to the battery technology as different capacity values are achieved by using different battery technologies.

The CCONTs A/D converter input measures the battery voltage, temperature, size and current.

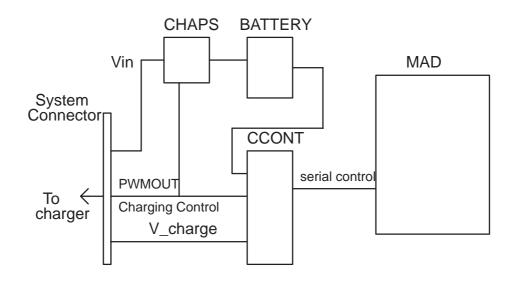

**NOTE:** Power management circuitry controls the charging current delivered from the charger to the battery. Charging is controlled with a PWM input signal from CCONT. The pulse width is controlled by MAD4 and is sent to CCONT through a serial bus. The battery voltage rise is limited by turning CHAPS switch off when the battery voltage has reached the desired limits.

#### Watchdog

MAD4 must reset the CCONT watchdog regularly. CCONT watchdog time can be set through SIO between 0 and 63 seconds at 1 second steps. Af-

ter power–up the default value is 32 seconds. If the watchdog expires, CCONT will cut off all supply voltages. After total cut–off the phone can be re–started through any normal power–up procedure. CCONTs watcdog functionality may be temporarily disabled by holding CCONTs PWRONX/WDDISX pin at logic low.

#### **Power Up**

There are four ways to power on the phone.

- 1. Pressing the power button

- 2. Connecting a charger

- 3. An IBI interrupt on BTEMP

- 4. Internal RTC times out.

Each of four methods is described in general in the following sections.

When the battery is connected to phone, nothing will happen until the power–up procedure is initiated, for instance by pressing the power–button or by connecting a charger. After that the 32kHz crystal oscillator of CCONT is started (can take up to 1 sec), and the default regulators are powered up.

If a power down is done and the battery remains connected, the 32 kHz crystal oscillator keeps running in the CCONT.

Power distribution diagram

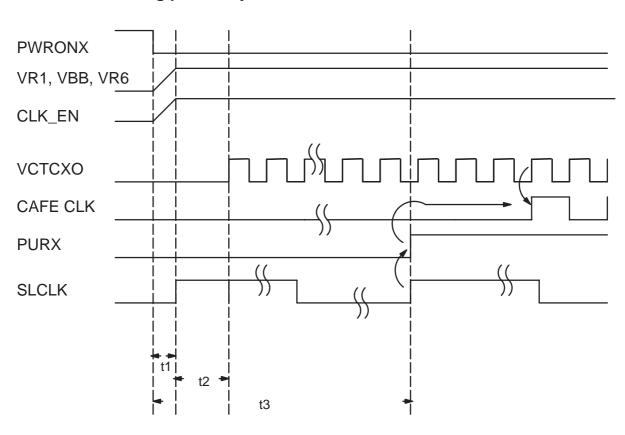

Pressing power key

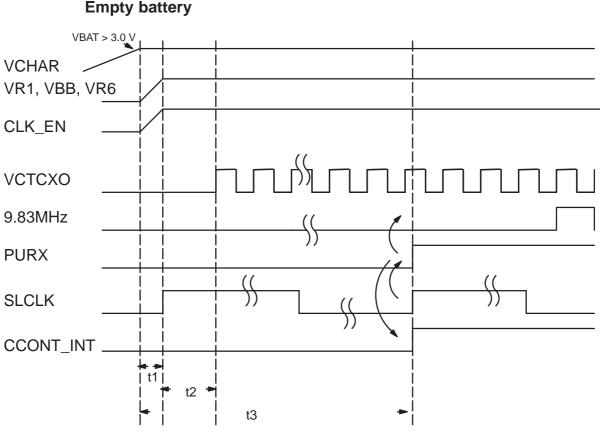

| t1 | < 1 ms                               |

|----|--------------------------------------|

| t2 | 1 – 6 ms, VCXO settled               |

| t3 | 62 ms, PURX delay generated by CCONT |

After PWR-key has been pushed, CCONT gives PURX reset to MAD4 and turns on VR1, VBB and VR6 regulators (if battery voltage has exceeded 3.0 V). VR1 supplies VCTCXO, VBB supplies MAD, and VR6 supplies digital parts of CAFE. After the initial delay, t2, VCTCXO starts to give a proper 19.2MHz clock to CAFE, which further divides it to 9.83MHz for MAD4. CAFE will output the 9.83MHz clock only after the PURX reset has been removed. After delay, t3, CCONT releases PURX and MAD4 can take control of the operation of the phone.

After MAD4s reset is released MCU–SW detects that the PWR–key is still pushed and shows the user that the phone is powering up by turning on the LCD and the lights. MCU–SW then powers up the RF receiver part.

V5V–regulator (for RF) default value is off in power–up, and can be controlled on via serial bus when needed.

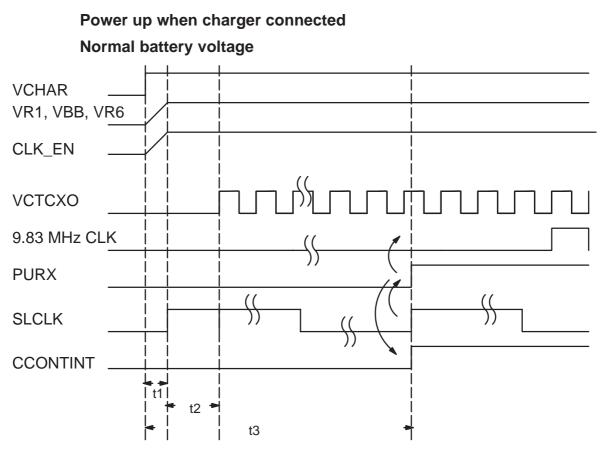

Power up, charger connected, VBAT > 3.0 V

The power up procedure is similar to the process described in the previous chapter with the exception that the rising edge of VCHAR triggers the power up in CCONT.

CCONT sets output CCONT\_INT, MAD4 detects the interrupt and reads CCONT status register to find the reason for the interrupt (charger in this case). After reading the A/D register to determine that the charger voltage is correct MAD should initiate charging activities. The phone will remain in the so called "acting dead" state which means that only the battery bars are displayed on the LCD. The user perceives that the phone is off. If the power on button is pushed the LCD display will come on and startup will be the same as normal power on.

CCONT\_INT is generated both when the charger is connected, and when the charger is disconnected.

Power up, charger connected, VBAT < 3.0 V

Before battery voltage voltage rises over 3.0 V CHAPS gives an initial charge (with limited current) to the battery. After battery voltage reaches 3.0V the power up procedure is as described in the previous section.

If a power down is done and the battery remains connected, the 32 kHz crystal oscillator keeps running in the CCONT. When a power–up is initiated again, the complete power–up sequence is described in the figure below. This time the power–up sequence is faster because the oscillator is already running.

#### Charging – CHAPS

CHAPS comprises the hardware for charging the battery and protecting the phone from over–voltage in charger connector.

The main functions are:

-transient, over-voltage and reverse charger voltage protection

-limited start-up charge current for a totally empty battery

-voltage limit when battery removed

-with SW protection protection against too high charging current

CHAPS is basically a PWM (Pulse Width Modulation) controlled switch which connects the charger to VBAT. MAD4 controlls CHAPS by writing PWM values to CCONTs PWM register over a serial bus. CCONT then outputs a PWM which is used by CHAPS to control the switch. In the case of an external fast charger, the PWM is available at the system connector to control the charger. In the case of a dead battery, shorted battery, or if the battery is below 3.0V, CHAPS supplies a controlled leakage current of about 180mA through the switch to attempt to bring the battery voltage up.

| Pin<br>num-<br>ber                  | Name   | Description                                                          |  |

|-------------------------------------|--------|----------------------------------------------------------------------|--|

| 1, 16                               | VCH    | Charger voltage input                                                |  |

| 5                                   | RSENSE | High current output, connected to current sense<br>resistor of phone |  |

| 12                                  | VBAT   | Battery voltage (connected to voltage sense part of CHAPS)           |  |

| 10                                  | VBACK  | Backup battery charging voltage output                               |  |

| 9                                   | LIM    | Output voltage limit select input                                    |  |

| 7                                   | PWM    | Charging switch control input                                        |  |

| 8                                   | CTIM   | External capacitor for soft switching                                |  |

| 2, 3, 4,<br>6, 11,<br>13, 14,<br>15 | GND    | Ground                                                               |  |

#### 2-wire charging

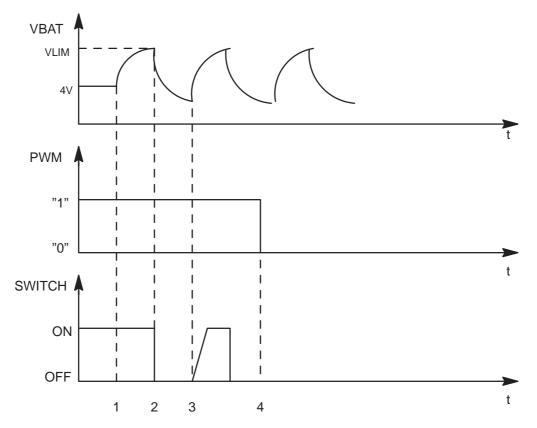

With 2–wire charging the charger provides constant output current, and the charging is controlled by PWMOUT signal from CCONT to CHAPS. PWMOUT signal frequency is selected to be 1 Hz, and the charging switch in CHAPS is pulsed on and off at this frequency. The final charging current to the battery is controlled by adjusting the PWMOUT signal pulse width.

Both the PWMOUT frequency selection and pulse width control are made by the MCU which writes these values to CCONT. The 2–wire charger is part number ACP–7, has full–wave rectified output, defined output voltage and impedance. Typical output current into empty battery is about 350 mA at nominal mains voltage.

#### 3–wire charging

With 3–wire charging the charger provides adjustable output current, and the charging is controlled by PWMOUT signal from CCONT to Charger, with the bottom connector signal. PWMOUT signal frequency is selected to be 32 Hz, and the charger output voltage is controlled by adjusting the PWMOUT signal pulse width. The charger switch in CHAPS is constantly on in this case.

The 3–wire charger is part number ACP–9, a switchmode power supply (SMPS) adapter using 3–wire charging structure (controlled constant voltage). Typical output into an empty battery is about 850mA at nominal mains voltage.

#### Battery disconnected when charger is connected

From hardware point of view the phone could otherwise continue functioning normally, but if the charger voltage is higher than the maximum allowed battery voltage, this can damage the RF parts. Therefore, output overvoltage protection is needed in case the battery is removed when a charger is connected, or if a charger is connected before the battery to the phone. With a charger connected, if VBAT exceeds preset limits in CHAPS, the switch turns OFF immediately (soft switching bypassed). There are two voltage limits, VLIM1 and VLIM2. VLIM input = '0' selects VLIM1, VLIM input = '1' selects VLIM2.

| Parameter                                                       | Symbol | Min | Тур | Max | Unit |

|-----------------------------------------------------------------|--------|-----|-----|-----|------|

| Output voltage cutoff limit (during transmission or Li–battery) | VLIM1  | 4.4 | 4.6 | 4.8 | V    |

| Output voltage cutoff limit (no transmission or Ni–battery)     | VLIM2  | 4.8 | 5.0 | 5.2 | V    |

When the switch turns off due to an overvoltage condition, it stays off until the input voltage falls below the specified limit (VCH<VBAT). Phone software will stop the charging as fast as it detects that there is no battery present.

- 1. Battery removed, (standard) charger connected, VBAT rises (follows charger voltage)

- 2. VBAT exceeds limit VLIM(X), switch is turned immediately OFF

- VBAT falls (because no battery), also VCH<VBAT (standard chargers full-rectified output). When VCH > VBAT and VBAT < VLIM(X) -> switch turned on again (also PWM is still HIGH) and VBAT exceeds VLIM(X).

- 4. Software sets PWM = LOW -> CHAPS does not enter PWM mode

Output overvoltage protection when battery removed ( in principle )

#### **Power Down**

#### Pushing power key

When the user wishes to turn the phone off and presses the power key, MAD (MCU SW) detects that PWR–key is pressed for a long enough time. After that the lights and LCD are turned off. MCU stops all the activities it was doing (e.g. ends a call), sends power off command to CCONT by writing a 'zero' amount of time to the watchdog register, and goes to idle–task. After the delay CCONT cuts all the supply voltages from the phone. Only the 32 kHz sleep clock remains running.

Note that the phone doesn't go to power off (from HW point of view) when the charger is connected and PWR–key is pushed. The user perceives that the phone is off, but in fact the phone is just acting as if it is off (this state is usually called "acting dead").

#### **Battery charge low**

As a battery discharges, energy management software keeps a constant watch on the voltage and displays an appropriate amount of battery bars.

When the battery discharges to a critical level the software notifies the user by beeping. If left on, the software will power off the phone at a VBAT of *TBD* V.

If the SW fails to power down the phone, hardware will take over and CCONT will do a reset and power down the phone when the battery voltage drops below 2.8 V.

#### Watchdog expires

If the SW fails to update the watchdog, the watchdog will eventually expire and CCONT cuts all the supply voltages to the phone. On startup, the initial value set in CCONT's watchdog timer register is 32.5 seconds. The watchdog is programmable from 0 to 63 seconds.

#### **Disconnected battery**

When battery is disconnected, immediate and totally uncontrolled powerdown happens. Therefore a power off procedure in this case can not be described. One possible risk is that if the MCU is writing something to the EEPROM exactly at the same moment, the memory contents may be corrupted.

#### **RF to Baseband Interface**

The RF to Baseband interface consists of MAD4 and CAFÉ communicating with various parts of the RF module. The MAD4 ASIC produces the Pulse Duration Modulators (PDMs) which allow analog voltages to be used for RF control. It also controls the VCTCXO enable, as well as band and mode selects. MAD also controls the RF supply voltages through CCONT. The CAFÉ ASIC performs the A/D and D/A conversions for CDMA and AMPS RX and TX paths. CAFÉ also receives the VCTCXO 19.2 MHz signal and provides MAD4 with the 19.2 MHz system clock.

## **Audio control**

#### **Audio Controls and Processing**

The audio control is handled by the MAD4 MCU. Speech coding functions are performed in MAD4 DSP. In transmission mode, the speech code is then sent to the CAFÉ ASIC for D/A conversion. In receiver mode, PCM coded blocks are read from the CAFE ASIC Both audio and RF CO-DECs reside in CAFÉ.

#### Earpiece

The internal earpiece is connected to the UI board by means of mounting springs for automated assembly. The 32–ohm impedance, dynamic type earpiece is connected to the differential output of the CAFÉ ASIC.

#### Microphone

The internal microphone is connected to the bottom connector by means of mounting springs. The microphone bias is provided by the CAFÉ ASIC.

#### Audio Accessory Interface

External audio is interfaced to the phone through the system connector. XEAR, XMIC, and SGND are the phone's external audio signal pins used for communication during a hands free accessory call.

## **Digital control**

#### MAD4

The baseband functions are controlled by the MAD asic, which consists of a MCU, a system ASIC and a DSP. The CDMA specific asic is named as MAD4.

#### MCU

For general purpose processing applications.

#### DSP

The DSP is in charge of the channel and speech coding. The Main interfaces are to the MCU, and via System Logic to CAFE and RF.

#### System Logic

Peripheral interface:

• MCU Parallel I/O, UART, and PWM control (PUP)

Serial Accessory Interface (FBUS):

- Autobauding support (Acclf)

- Interface to external memories

- Address lines and chip select decoding (BUSC)

- RF Interface and Control (RFIfCtrl)

- Clocking, timing and interrupts (CTI)

- Sleep Control (SleepBlk)

- CAFE Control (CAFECtrl)

User Interface Control (UserIf)

Reset Generator (RstGen)

Clock Generator (ClkGen)

Test Interface (TestIf)

#### **MAD Interfaces**

#### **UI and CCONT Serial interface**

MAD4s serial interface is used to control the Serial LCD on the User Interface board, and to provide access to CCONTs registers. The DataSelX and DataClk are generated by MAD4 during both transmit and receive cycles. Each device has its own chip select signal and must hold its data pin in a high impedance state if its chip select is not active. Data must be valid on the rising edge of DataClk during both transmit and receive.

#### CAFE Interface

The MAD4 ASIC supplies an interface to the CAFE ASIC. This interface consists of parallel transmit and receive busses for CDMA and AMPS data, and a serial interface for Codec control and data.

#### FBUS

FBUS (Fast Bus) is a fast serial interface between the DSP and data accessories or the DSP and multipath analyzer. This interface is a full–duplex, asynchronous, two–line bus.

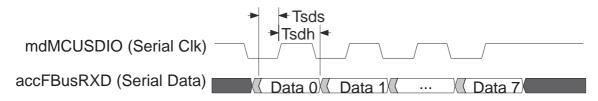

USART Synchronous Mode Receive (Flashing Mode)

#### MBUS

MBUS is the MCUs serial interface which is used for FLASH downloading (not program code), testing, and communication with external devices. Supported baud rates are 9.6, 19.2, 38.4 and 57.6 kbit/s.

#### JTAG Interface

The JTAG interface is used for MAD4 ASIC emulation. This interface provides for coemulation of the DSP and MCU.

#### TRUST Interface

TRUST (Trace Utility for Software Testing) is a hardware module used to capture tracing data from a phone during testing. It serves as a buffer memory, storing data from the address and data buses of the phone MCU until read by a PC. A time label is attached to each data word. The unit also includes a buffer for commands from the PC to the phone.

#### **Signal Definitions**

| SIGNAL NAME                    | DESCRIPTION                                                                        | From/To                              | Signal Charac-<br>teristics   | Notes |

|--------------------------------|------------------------------------------------------------------------------------|--------------------------------------|-------------------------------|-------|

| Busses, Strobes,<br>and Clocks | Includes parallel and serial<br>busses as well as data clocks,<br>and chip selects |                                      |                               |       |

| ADD(20:0)                      | 21–Bit Memory Address Bus                                                          | MAD4 to FLASH<br>and SRAM            | 0 to 2.8V Digital             |       |

| DATA(15:0)                     | 16–Bit Memory Data Bus                                                             | MAD4 to FLASH<br>and SRAM            | 0 to 2.8V Digital             |       |

| RXD(11:0)                      | Receive Data                                                                       | CAFE to MAD4                         | 0 to 2.8V Digital             |       |

| TXD(7:0)                       | Transmit Data                                                                      | MAD4 to CAFE                         | 0 to 2.8V Digital             |       |

| EEPROMSCLK                     | SCLK to serial EEPROM                                                              | MAD4 to EE-<br>PROM                  | 0 to 2.8V Digital             |       |

| EEPROMSDA                      | Serial data line for serial EE-<br>PROM.                                           | MAD4 to EE-<br>PROM                  | 0 to 2.8V Digital<br>(Pullup) |       |

| UIF_CCONT_SCLK                 | Clock for UI and CCONT serial interface                                            | MAD4 to<br>CCONT and UI<br>connector | 0 to 2.8V Digital             |       |

| UIF_CCONT_SDIO                 | User Interface and CCONT Seri-<br>al Data                                          | MAD4 to<br>CCONT and UI<br>connector | 0 to 2.8V Digital             |       |

| SIGNAL NAME            | DESCRIPTION                                    | From/To                       | Signal Charac-<br>teristics | Notes                                                           |

|------------------------|------------------------------------------------|-------------------------------|-----------------------------|-----------------------------------------------------------------|

| CCONTCSX               | CCONT Chip Select                              | MAD4 to<br>CCONT              | 0 to 2.8V Digital           |                                                                 |

| LCDCS                  | LCD Chip Select                                | MAD4 to UI con-<br>nector     | 0 to 2.8V Digital           |                                                                 |

| MEM(3)                 | Memory Read Strobe                             | MAD4 to FLASH<br>and SRAM     | 0 to 2.8V Digital           |                                                                 |

| MEM(2)                 | Memory Write Strobe                            | MAD4 to FLASH<br>and SRAM     | 0 to 2.8V Digital           |                                                                 |

| MEM(1)                 | RAM Chip Select                                | MAD4 to SRAM                  | 0 to 2.8V Digital           |                                                                 |

| MEM(0)                 | FLASH chip enable                              | MAD4 to FLASH                 | 0 to 2.8V Digital           |                                                                 |

| MBUS                   | MCU serial bus for external com-<br>munication | MAD4 to System connector      | 0 to 2.8V Digital           |                                                                 |

| FBUS_TX                | DSP Accessory UART Data Out-<br>put            | MAD4 to System connector      | 0 to 2.8V Digital           |                                                                 |

| FBUS_RX                | DSP Accessory UART Data In-<br>put             | System connec-<br>tor to MAD4 | 0 to 2.8V Digital           |                                                                 |

| ADATA                  | AMPS Data Input to RxModem<br>(MAD4)           | CAFE to MAD4                  | 0 to 2.8V Digital           |                                                                 |

| CAFESIO(2)             | CAFE I/F Frame Sync                            | MAD4 to CAFE                  | 0 to 2.8V Digital           |                                                                 |

| CAFESIO(1)             | CAFE I/F Serial Data from CAFE                 | CAFE to MAD4                  | 0 to 2.8V Digital           |                                                                 |

| CAFESIO(0)             | CAFE I/F Serial Data to CAFE                   | MAD4 to CAFE                  | 0 to 2.8V Digital           |                                                                 |

| CLK9M20                | 19.2MHz System Clock                           | CAFE to MAD4                  | 0 to 2.8V Digital           |                                                                 |

| CLK9M83                | 9.8304MHz CDMA Clock                           | CAFE to MAD4                  | 0 to 2.8V Digital           |                                                                 |

| SLEEPCLK               | 32.768kHz Sleep Clock                          | CCONT to<br>MAD4              | 0 to 2.8V Digital           | Oscillator still<br>running when<br>phone is pow-<br>ered down. |

|                        | RF Interface Control Signals                   |                               |                             |                                                                 |

| CAFE_TX_GATE           | Transmitter Gating Signal                      | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| TIF_EN                 | TIF chip enable                                | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| SYN_ACQ&SYN_P<br>WR_DN |                                                | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| SYN_LK1                |                                                | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| RIF_EN                 |                                                | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| TX_LIM                 | Indicates TX Power Greater than TXI_REF        | RF to MAD4                    |                             |                                                                 |

| SYN_CLK                | R/F I/F Serial Clock                           | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| SYN_DAT                | R/F I/F Serial Data                            | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| SYN_LE1                | R/F I/F Serial Latch Enable #1                 | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| CEL_MODE               | R/F I/F Serial Latch Enable #2                 | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| BAND_SEL               | RF Frequency Band Select (PCS or Cellular)     | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| MODE_SEL               | RF Mode Select (CDMA or AMPS)                  | MAD4 to RF                    | 0 to 2.8V Digital           |                                                                 |

| SIGNAL NAME  | DESCRIPTION                                                                                | From/To                                                                                 | Signal Charac-<br>teristics                                         | Notes                                                       |

|--------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------|

| AFC          | AFC PDM                                                                                    | MAD4 to RF                                                                              | 0 to 2.8V contin-<br>uously variable                                |                                                             |

| RX_IF_AGC    | Receive IF AGC PDM                                                                         | MAD4 to RF                                                                              | 0 to 2.8V contin-<br>uously variable                                |                                                             |

| TX_IF_AGC    | Transmit IF AGC PDM                                                                        | MAD4 to RF                                                                              | 0 to 2.8V contin-<br>uously variable                                |                                                             |

| TX_RF_AGC    | Transmit RF AGC PDM                                                                        | MAD4 to RF                                                                              | 0 to 2.8V contin-<br>uously variable                                |                                                             |

| TX_VCO_CAL   | PENTA Regulator control (P5)                                                               | MAD4 to RF                                                                              | 0 to 2.8V                                                           | Not used as a PDM                                           |

| TX_LIM_ADJ   | General Purpose PDM2                                                                       | MAD4 to RF                                                                              | 0 to 2.8V contin-<br>uously variable                                |                                                             |

| FILT_SEL     | General Purpose PDM3                                                                       | MAD4 to RF                                                                              | 0 to 2.8V Digital                                                   | Not used as a<br>PDM                                        |

| BOOST        | General Purpose PDM4                                                                       | MAD4 to RF                                                                              | 0 to 2.8V contin-<br>uously variable                                |                                                             |

| RX_GS        | RF Receive Gain Switch function                                                            | MAD4 to RF                                                                              | 0 to 2.8V Digital                                                   |                                                             |

| RF_TX_GATE_P | Transmitter Gating Signal (PCS Mode)                                                       | MAD4 to RF                                                                              | 0 to 2.8V Digital                                                   |                                                             |

| RF_TX_GATE_C | Transmitter Gating Signal (Cellu-<br>lar Mode)                                             | MAD4 to RF                                                                              | 0 to 2.8V Digital                                                   |                                                             |

| CLK_EN       | VCTCXO Enable (to CCont<br>"SLEEPX" input)                                                 | MAD4 to<br>CCONT                                                                        | 0 to 2.8V Digital                                                   | Signal to<br>CCONT which<br>controls regula-<br>tors to RF. |

| VLIM         | Used to select the max battery voltage for the charging circuit in CHAPS (VLIM1 or VLIM2). | MAD4 to CHAPS                                                                           | 0 to 2.8V Digital                                                   |                                                             |

|              | Peripherals, Accessory Inter-<br>face, and A/Ds                                            |                                                                                         |                                                                     |                                                             |

| BUZZER       | Buzzer PWM Output                                                                          | MAd4 to UI con-<br>nector                                                               | 0 to 2.8V Digital                                                   |                                                             |

| VIBRA        | PWM output for vibra motor                                                                 | MAD4 to on<br>board VIBRA cir-<br>cuit, and to bat-<br>tery connector<br>via BTEMP line | 0 to 2.8V Digital                                                   |                                                             |

| HOOKINT      | Hook Interrupt                                                                             | CAFE to MAD4                                                                            | 0 to 2.8V Digital                                                   |                                                             |

| EAD_HEADINT  | Headset Interrupt (CCONT per-<br>forms A/D on this signal).                                | CAFE to MAD4<br>and CCONT                                                               |                                                                     |                                                             |

| tp4          | DBUS data line test point                                                                  | MAD4                                                                                    | 0 to 2.8V Digital                                                   |                                                             |

| RS232_PWR    | Control for switching power onto SGND while using a data cable accessory.                  | N306 (regulator)<br>to System con-<br>nector                                            | 0 to 2.8V Digital                                                   | Controlled by<br>MAD4                                       |

| BSI          | Intelligent Battery Interface. A/D input to CCONT.                                         | Battery connec-<br>tor to CCONT                                                         | DC voltage level<br>that varies with<br>different battery<br>types. | Voltage divider<br>A/D input to<br>CCONT                    |

**NOKIA** PAMS Technical Documentation

| SIGNAL NAME | DESCRIPTION                                                                                                                                                 | From/To                                      | Signal Charac-<br>teristics                                            | Notes                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|

| BTEMP       | A/D input to CCONT. Used for battery temperature detection and battery VIBRA control.                                                                       | Battery Connec-<br>tor to CCONT              | DC voltage level<br>which changes<br>with battery tem-<br>perature.    | Thermistor volt-<br>age divider A/D<br>input to CCONT |

| PA_TEMP     | A/D input to CCONT. Used for<br>RF power amp temperature<br>detection.                                                                                      | RF to CCONT                                  | DC voltage level<br>which changes<br>with PA tempera-<br>ture.         | Thermistor volt-<br>age divider A/D<br>input to CCONT |

| RSSI        | A/D input to CCONT. Receive signal strength indicator for AMPS mode.                                                                                        | RF to CCONT                                  | DC voltage level<br>which changes<br>with received<br>signal strength. |                                                       |

| V_IN        | Power in from charger                                                                                                                                       | System connec-<br>tor to CHAPS               | ACP–9 DC<br>ACP–7 Rectified<br>AC                                      | Voltage will<br>change with<br>charge control<br>PWM. |

| L_GND       | Ground reference for charger<br>(Separated from GND through<br>an inductor).                                                                                | System connec-<br>tor to GND via<br>inductor | 0V                                                                     |                                                       |

|             | Regulator Control Signals                                                                                                                                   |                                              |                                                                        |                                                       |

| VREGP1      | Controls voltage regulator P1 (PENTA).                                                                                                                      | MAD4 to<br>CCONT                             | 0 to 2.8V Digital                                                      |                                                       |

| VREGP2      | Used to control voltage regulator<br>P2 (PENTA). This signal is also<br>the MSB (bit–21) of the Memory<br>Address Bus but is not used as<br>an address bit. | MAD4 to<br>CCONT                             | 0 to 2.8V Digital                                                      |                                                       |

| VREGP3      | Controls voltage regulator P3 (PENTA).                                                                                                                      | MAD4 to<br>CCONT                             | 0 to 2.8V Digital                                                      |                                                       |

| VREGP4      | Controls voltage regulator P4 (PENTA).                                                                                                                      | MAD4 to<br>CCONT                             | 0 to 2.8V Digital                                                      |                                                       |

| CCONT_INT   | CCONT interrupt to MAD4                                                                                                                                     | CCONT to<br>MAD4                             | 0 to 2.8V Digital                                                      |                                                       |

|             | User Interface Board Peripher-<br>als                                                                                                                       |                                              |                                                                        |                                                       |

| FLIP        | Flip interrupt (detects status of hinge) on variants with flip fea-<br>ture.                                                                                | UI connector to<br>MAD4                      | 0 to 2.8V Digital                                                      |                                                       |

| BACKLIGHT   | Controls illumination on UI board.                                                                                                                          | MAD4 to UI con-<br>nector                    | 0 to 2.8V Digital                                                      |                                                       |

| CALL_LED    | Controls the call LED on UI board.                                                                                                                          | MAD4 to UI con-<br>nector                    | 0 to 2.8V Digital                                                      |                                                       |

| LCD_RESETX  | Resets the LCD on the UI board.                                                                                                                             | MAD4 to UI con-<br>nector                    | 0 to 2.8V Digital                                                      |                                                       |

| COL(4:0)    | Keyboard Columns on UI board.                                                                                                                               | MAD4 to UI con-<br>nector                    | 0 to 2.8V Digital                                                      |                                                       |

| UIF(5:0)    | Keyboard Rows and LCD I/F                                                                                                                                   | MAD4 to UI con-<br>nector                    | 0 to 2.8V Digital                                                      |                                                       |

| SIGNAL NAME   | DESCRIPTION                                                                                                                         | From/To                    | Signal Charac-<br>teristics          | Notes                                        |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------|----------------------------------------------|

| PWRONX        | Power button signal                                                                                                                 | UI connector to<br>MAD4    | 0 to 2.8V Digital                    |                                              |

| Resets        |                                                                                                                                     |                            |                                      |                                              |

| PURX          | Power Up Reset                                                                                                                      | CCONT to<br>MAD4           | 0 to 2.8V Digital                    |                                              |

| RESETX        | System Reset                                                                                                                        | MAD4 to CAFE               | 0 to 2.8V Digital                    |                                              |

| CAFE RF/IF    |                                                                                                                                     |                            |                                      |                                              |

| IQSEL         | IQ Select control line for select-<br>ing I or Q data                                                                               | MAD4 to CAFE               | 0 to 2.8V Digital                    |                                              |

| RXIQ(3:0)     | CDMA Receive I and Q data                                                                                                           | RF to CAFE                 | Differential I and Differential Q    |                                              |

| TXIQ(3:0)     | CDMA Transmit I and Q data                                                                                                          | CAFE to RF                 | Differential I and<br>Differential Q |                                              |

| LIM_P         | non–inverting AMPS receive modulated signal                                                                                         | RF to CAFE                 | analog                               |                                              |

| LIM_N         | Inverting AMPS receive modu-<br>lated signal                                                                                        | RF to CAFE                 | analog                               |                                              |

| CLK19M2RF     | 19.2MHz sinusiod from RF                                                                                                            | RF to CAFE                 | sinusoid                             |                                              |

| AMPSMOD       | AMPS audio signal (after DSPand D/A) to be transmitted.                                                                             | CAFE to RF                 | analog (voice)                       |                                              |

|               | Test & Emulation                                                                                                                    |                            |                                      |                                              |

| JTAG1_TRST    | JTAG Reset                                                                                                                          | MAD4                       | 0 to 2.8V Digital                    |                                              |

| JTAG2_TDI     | JTAG Scan Input                                                                                                                     | MAD4                       | 0 to 2.8V Digital                    |                                              |

| JTAG3_TDO     | JTAG Scan Output                                                                                                                    | MAD4                       | 0 to 2.8V Digital                    |                                              |

| JTAG4_TCK     | JTAG Clock & ATPG Scan Clock                                                                                                        | MAD4                       | 0 to 2.8V Digital                    |                                              |

| JTAG5_PD      | JTAG Mode Select & ATPG<br>Scan Enable                                                                                              | MAD4                       | 0 to 2.8V Digital                    |                                              |

| JTAG0         | DSP/MCU Emulation (NOT<br>USED)                                                                                                     | MAD4                       | 0 to 2.8V Digital                    |                                              |

| JTAG6         | DSP/MCU Emulation (NOT<br>USED)                                                                                                     | MAD4                       | 0 to 2.8V Digital                    |                                              |

|               | DSP External Flag<br>(NOTE: This pin has a dual func-<br>tion as General Purpose I/O<br>"P0GPIO(6)". DSPXF is default<br>function.) | MAD4                       | 0 to 2.8V Digital                    |                                              |

| CHRG_CTRL_A   | DSP Serial Port Input Clock (for multipath analyzer)                                                                                | MAD4                       | 0 to 2.8V Digital                    |                                              |

| TP5           | DSP Serial Port Frame Sync(for multipath analyzer)                                                                                  | MAD4                       | 0 to 2.8V Digital                    |                                              |

| WDDIS         | Watchdog Disable                                                                                                                    | Test Connector<br>to CCONT | 0 to 2.8V Digital                    | Used in factory<br>while still in pan-<br>el |

| CCONT Outputs |                                                                                                                                     |                            |                                      |                                              |

| SIGNAL NAME   | DESCRIPTION                                                                           | From/To                                                             | Signal Charac-<br>teristics | Notes                                                                        |

|---------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------|

| VBB           | LEAD power pins (DSP)                                                                 | CCONT to<br>MAD4 and me-<br>mories as the UI<br>connector           | 2.8V regulator              |                                                                              |

| VR1_SW        | Power for microphone bias                                                             | CCONT to V201<br>(CAFE)                                             | 2.8V regulator              |                                                                              |

| VR1           | Provides RF power                                                                     | to RF                                                               | 2.8V regulator              |                                                                              |

| VR2           | Provides RF power                                                                     | to RF                                                               | 2.8V regulator              |                                                                              |

| VR3           | Provides RF power                                                                     | to RF                                                               | 2.8V regulator              |                                                                              |

| VR4           | Provides RF power                                                                     | to RF                                                               | 2.8V regulator              |                                                                              |

| VR5           | Provides RF power                                                                     | to RF                                                               | 2.8V regulator              |                                                                              |

| VR6           | Provides power to CAFE                                                                | to RF                                                               | 2.8V regulator              |                                                                              |

| VR7           | Provides RF power                                                                     | to RF                                                               | 2.8V regulator              |                                                                              |

| VR7A          | provides RF power                                                                     | to RF                                                               | 2.8V regulator              | regulator exter-<br>nal to CCONT                                             |

| VREF          | Used by CAFE as an A/D volt-<br>age reference                                         | to CAFE                                                             | 1.244V reference            |                                                                              |

| VMAD          | Provides power to the MAD4 core. Will be used only with the ROM3 version of MAD4.     | CCONT to<br>MAD4                                                    | 1.8V regulator              | Programmable to different voltages                                           |

| +5V_POWER     | Provides 5V power to RF                                                               | to RF                                                               | 4.7 to 5.2V                 | Charge pump                                                                  |

| 3V_5V         | Provides 3V to flash (Vpp) for programming                                            | CCONT to<br>FLASH                                                   | 2.7 to 3.3V                 | used at 3V                                                                   |

| CHRG_CTRL     | Charge control PWM signal for accessories                                             | System connec-<br>tor to CHAPS.<br>Can also be driv-<br>en by CCONT | 0 to 2.8V Digital           |                                                                              |

| Audio Signals |                                                                                       |                                                                     |                             |                                                                              |

| EARN          | Inverting part of the audio differ-<br>ential signal to the earpiece.                 | CAFE to UI con-<br>nector                                           | 1.8Vp–p max                 | combined differ-<br>ential output<br>from earn and<br>earp is 3.6Vp–p<br>max |

| EARP          | Non-inverting part of the audio differential signal to the earpiece.                  | CAFE to UI con-<br>nector                                           | 1.8Vp–p max                 | combined differ-<br>ential output<br>from earn and<br>earp is 3.6Vp–p<br>max |

| XEAR          | Single ended audio signal to bot-<br>tom connector.                                   | CAFE to System connector                                            | 1.8Vp–p max                 | single ended                                                                 |

| MICP          | Non–inverting part of the audio<br>differential signal to the internal<br>microphone. | System connec-<br>tor (mic) to<br>CAFE                              | Can be used up<br>to 1Vp–p  | combined differ-<br>ential input from<br>MICP and MICN<br>is 2Vp-p max       |

| SIGNAL NAME | DESCRIPTION                                                                           | From/To                                   | Signal Charac-<br>teristics                | Notes                                                                  |

|-------------|---------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------|------------------------------------------------------------------------|

| MICN        | Inverting part of the audio differ-<br>ential signal to the internal micro-<br>phone. | System connec-<br>tor (mic) to<br>CAFE    | Can be used up<br>to 1Vp–p                 | combined differ-<br>ential input from<br>MICP and MICN<br>is 2Vp–p max |

| XMIC        | Single ended external audio in-<br>put from the bottom connector.                     | System connec-<br>tor to                  | Can be used up<br>to 1Vp–p                 |                                                                        |

| SGND        | Return path for accessory audio, and power for data cable.                            | System connec-<br>tor to CAFE and<br>N306 | nearly 0V. Has<br>some AC com-<br>ponents. | Capacitively<br>coupled input to<br>CAFE. Resistive<br>pulldown        |

#### CAFE Submodule

#### **CDMA RX**

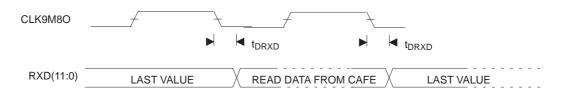

The MAD/CAFE RX Interface consists of a 12–bit data bus RXD(11:0) output from the CAFE ASIC to the MAD ASIC. In CDMA mode the data transfer rate is 9.8304MHz. The RX data is clocked out of the CAFE ASIC on the falling edge of the 9.8304MHz clock, and clocked into the MAD ASIC on the rising edge. For CDMA mode the 4–bit RXI data is supplied on bits RXD(5:2) and the 4–bit RXQ data is supplied on bits RXD(11:8). Bits (7), (6), (1) and (0) are not used in CDMA mode.

Digital Mode RX Data Bus Timing

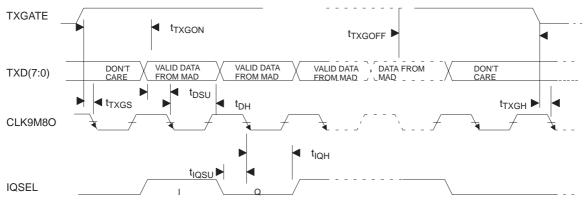

## CDMA TX

CDMA TX data is transferred from MAD4 to CAFE by using an 8–bit multiplexed parallel data bus TXD(7:0). The data is clocked out of MAD on the rising edge of the clock and clocked into the CAFE on the falling edge of the clock. The bus data rate is 9.8304 MHz.

Digital Mode TX Data Bus Timing

## AMPS RX

AMPS receive data from the RF section is differential, through pin 23 and 24 of the CAFE ASIC. RX data is transferred at 40 kHz through a 12–bit data bus RXD(11:0) output from the CAFE ASIC to the MAD4 ASIC. Wide band data (ADATA) is one bit asynchronous data running at 150 kHz.

Data conversion and the bus interface is synchronous. Data is clocked out of CAFE on the falling edge of the clock and clocked into the MAD4 on the rising edge of the clock.

## AMPS TX

The TX data in AMPS mode is transferred at 120 kHz using an 8–bit multiplexed parallel data bus TXD(7:0). The AMPS transmit channel uses the Q channel. TX data is clocked out of MAD4 on the rising edge and clocked into the CAFE on the falling edge.

CAFE and Peripherals Block Diagram

## Audio CODEC

The audio CODEC has the following functional blocks:

- 8 kHz interface for speech codec

- Microphone amplifiers and mux for 3 differential microphone inputs

- Variable gain amplifier for TX audio

- Variable gain amplifier for sidetone audio

- 13 bit Analog to Digital converter and lowpass filter

- 13 bit Digital to Analog converter and lowpass filter

- Variable gain amplifier for RX audio

- Speaker amplifiers for 3 speakers

#### Transmit

The microphone signal, MICP and MICN, is sent to CAFE differentially through pin 66 and pin 69. The maximum input signal level at either input is 1.0 V, which gives a differential level of 2.0  $V_{pp}$ . Audio data is transferred in 16 bit frames (2 LSBs are not used).

The audio signal from an external accessory (XMIC) drives pin 68. The ground reference for XMIC is SGND (pin 67), which is a virtual ground.

#### Receive

The audio receive path consists of a D/A converter, lowpass filter and output attenuator with three selectable outputs. Only one output can be active at a time. The biasing at the outputs can be independently controlled to be ON at all outputs to avoid switching transients.

The EAR output from pin 77 and pin 80 is intended to drive a phone earpiece having typically 32 ohm resistance. The output is differential, having positive (EARP) and negative (EARN) output terminals.

The HF output is intended to drive external audio circuitry via XEAR. The output is single–ended, but also has another pin (HFCM) which drives signal ground for it.

#### Detection

The external microphone input is detected by the voltage divider between R205 and R219 (EAD\_HEADINT, A/D to by CCONT). When XEAR is loaded, it can pull down R213 and generate an interrupt to MAD4 (HOOK-INT).

#### External Microphone Biasing

AUXOUT is used to generate biasing voltage for the external microphone, and will provide 1.5 V bias voltage to the external microphone. If AUX-OUT is not selected, the output will be in high impedance state.

R202, R220, C212, and V201 provide an alternative means of biasing the internal microphone.

## **EMC Strategy**